Cmos Circuit Diagram Of 1-bit Full Adder

Low-power_1-bit_cmos_full_adder_using_subthreshold_conduction_region Majority generator carry Cmos 1-bit full adder circuit (adapted from [7]).

Electrical – CMOS Adder circuits – Valuable Tech Notes

Full adder Electrical – cmos adder circuits – valuable tech notes Circuitos sumadores cmos

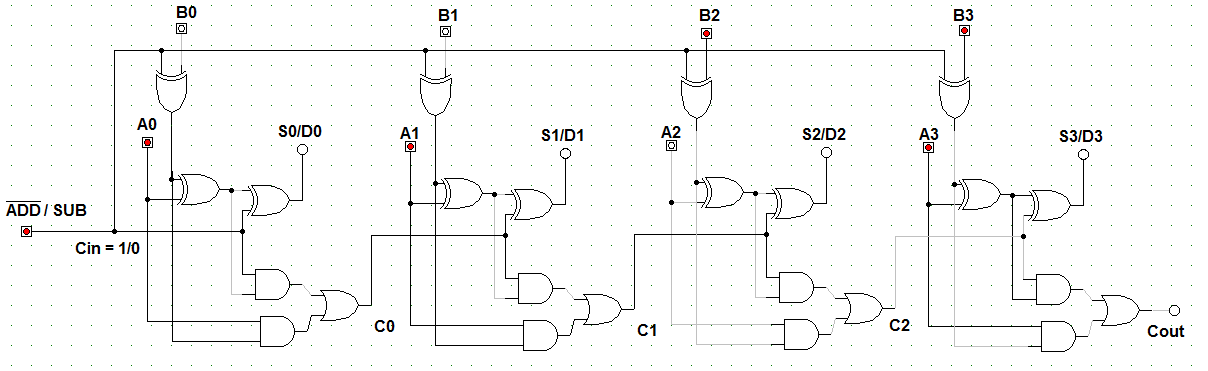

4-bit full adder circuit diagram

Cmos adder comparative logicDesign a cmos full-adder circuit with inputs a, b, Circuit diagram full adder using cmosCircuit diagram of a one-bit full adder using the proposed technique in.

Half adder vlsi cmosOn the design of high-performance cmos 1-bit full adder circuits Carry generator (majority function) circuit.Full adder circuit diagram using cmos wiring diagram schemas.

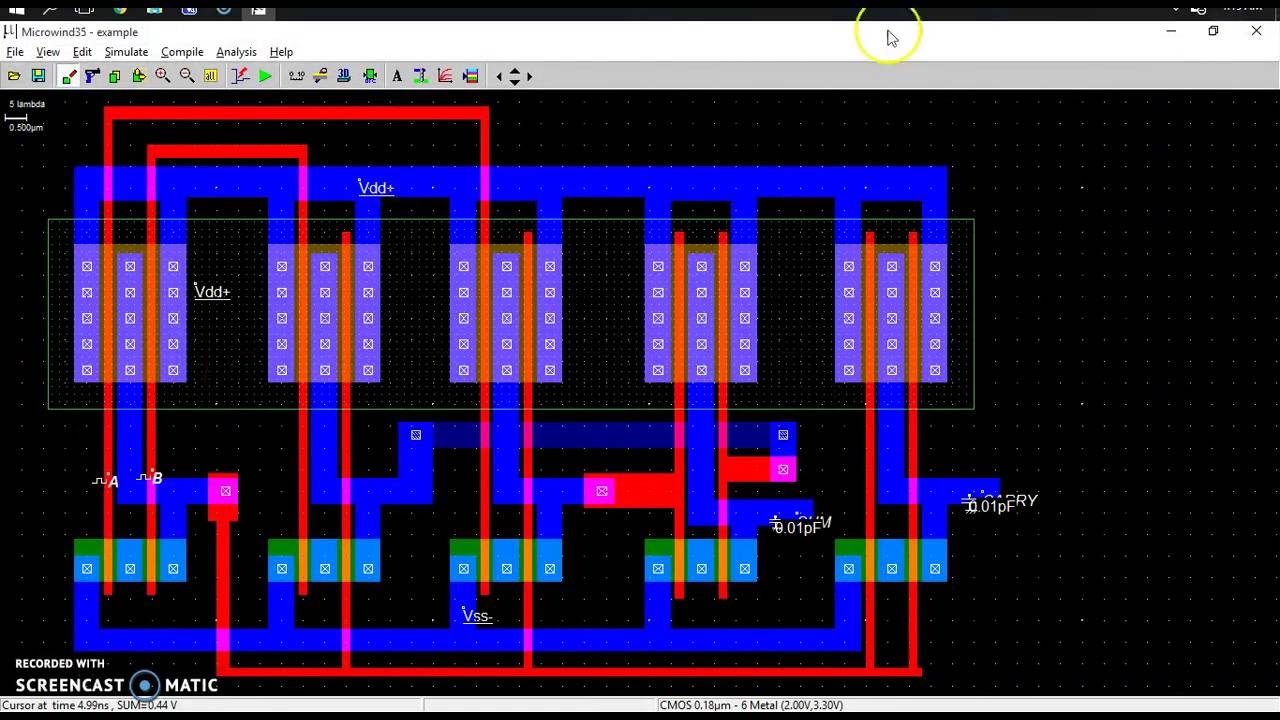

Tsmc 180 nm cmos full adder in lt spice measurement of delay and power

Implemented half adder using cmos transmission gates [1].[diagram] logic diagram 4 bit multiplier 4 bit binary adder circuit diagramCmos adder circuit solved transcribed.

4 bit adder pin diagramCircuit diagram full adder using cmos Full adder circuit – how it works2 bit adder circuit.

Explain full adder with circuit diagram

1 bit full adder logic diagramCommonly used bit full adder cells a conventional cmos full adder Implement half adder circuit using static cmos.Adder half cmos using circuit implement sum carry.

Cmos half adder circuit diagramAdder cmos bit full subthreshold conduction region low power using structure basic 4 bit adder circuit diagramA high speed low noise cmos dynamic full adder cell.

Cmos adder inputs circuit xor majority circuits

Solved 6. create a cmos circuit to create a half-adder, or aAdder sum simplified logic combinational circuits Adder cmos soi proposed techniqueFull adder circuit diagram with logic ic.

(pdf) low-power and high-performance 1-bit cmos full adder cell1 bit full adder cmos circuit Adder full cmos dynamic cell speed high figure noise lowA comparative study of full adder using static cmos logic style.

Schematic diagram of existing half adder using static cmos technique

Adder cmos conventionalConventional cmos full-adder, fa28t .

.

Electrical – CMOS Adder circuits – Valuable Tech Notes

Implement half adder circuit using static CMOS.

TSMC 180 nm CMOS Full Adder in LT Spice Measurement of Delay and Power

Circuit Diagram Full Adder Using Cmos

Conventional CMOS full-adder, FA28T | Download Scientific Diagram

Circuit diagram of a one-bit full adder using the proposed technique in

4-bit Full Adder Circuit Diagram